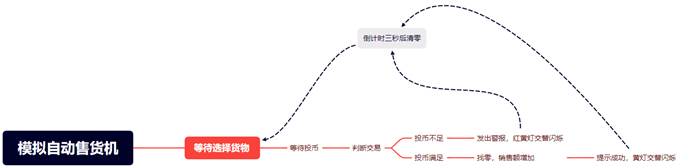

一 总体设计思想

1 总体流程

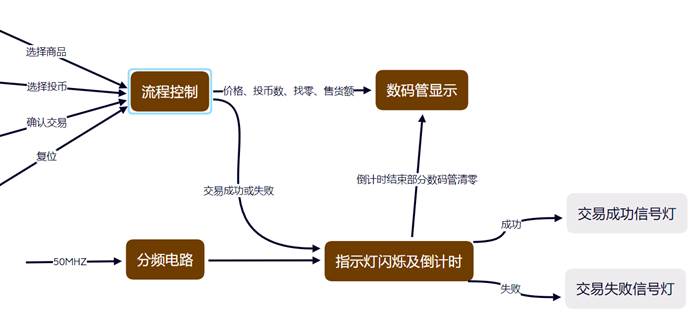

2 单元电路组成及功能

2.1 分频模块

由于50MHZ频率过高,指示灯闪烁和倒计时时间极短,肉眼看不出来,所以需要将FPGA板上的50MHZ时钟降频,获得一个周期0.2秒的脉冲。

2.2 指示灯闪烁及倒计时模块

当处于等待状态时,使八个黄灯按流水的方式闪烁,提示用户目前正在等待选择商品和投币

当处于交易成功状态时,使八个黄灯交替闪烁,提示用户目前已经交易成功

当处于警告状态时,使八个红灯和八个黄灯交替闪烁,提示用户投币不足,交易失败

利用0.2秒的脉冲连续计数15次获得三秒的倒计时,倒计时结束时将当前投币数清零

2.3 流程控制模块

负责整个售货机的流程控制,总共有四个状态:选择商品、选择投币、确认交易并判断交易结果、复位。

选择商品:可以通过拨动四个开关将其置1来选择买四种价格的商品,分别为10元、5元、2元、1元。

选择投币:可以通过拨动四个开关将其置1来选择投四种价格的硬币,分别为10元、5元、2元、1元。

确认交易:可以按动FPGA板右下角的一个按钮来确认进行交易,如果投入的硬币足够则交易成功并计算找零和售货额增加,如果投入的硬币不够则报警。

复位:可以按动FPGA板右下角的一个按钮来进行复位,将当前选择的商品、投入的硬币、找零数清零。

2.4 数码管显示模块

FPGA板共有8个数码管,选择左1、2数码管显示当前商品的价格,选择左3、4数码管显示当前投币数、选择左5、6数码管显示找零数、选择左7,8数码管显示总售货额。

二 系统逻辑框图

三 单元电路设计及总体电路设计图

1 分频模块

1 | module Divider |

2 流程控制模块

1 | module top_VendingMachine |

3 数码管显示模块

1 | module Display (hex_digit, segh,segl); |

4 指示灯闪烁及倒计时模块

1 | module Time |

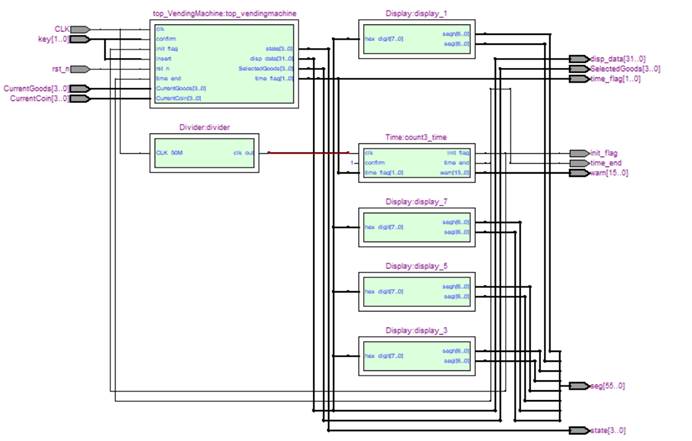

5 总体电路设计

1 | module VendingMachine |

6 顶层文件原理图

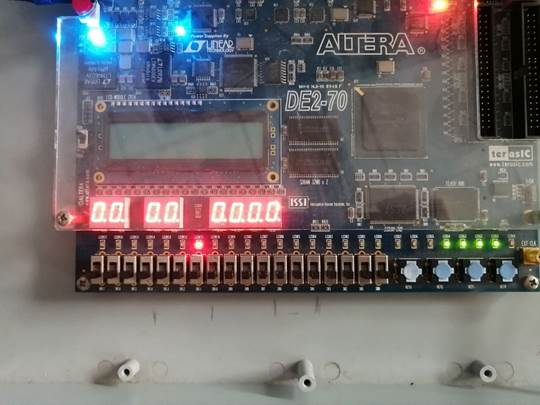

四 系统实现与调试

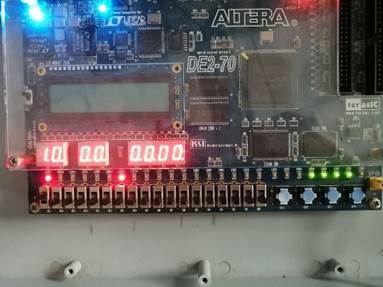

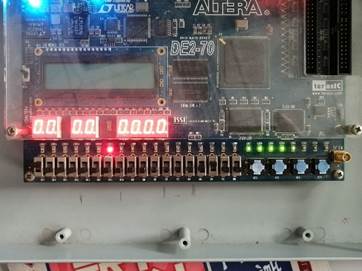

1 初始状态

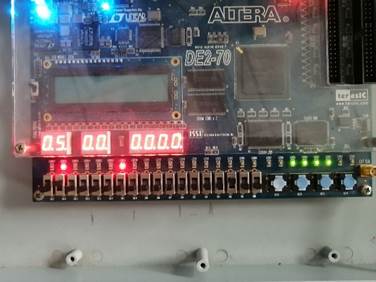

2 选择10元商品

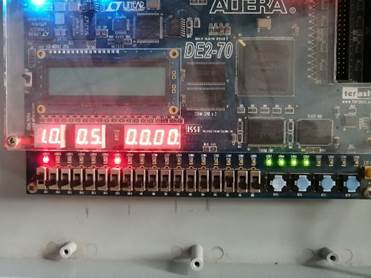

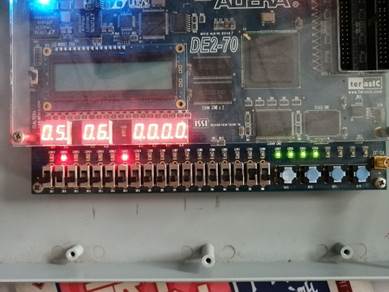

3 投币5元

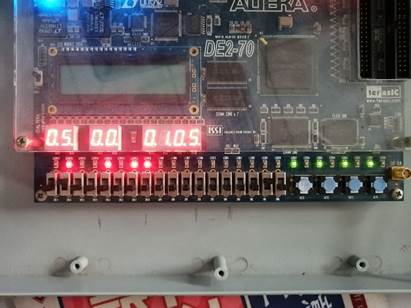

4 交易失败

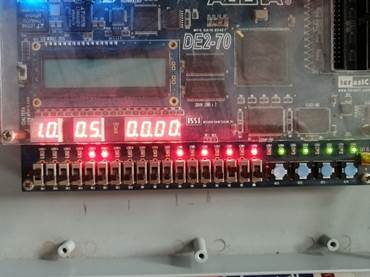

5 倒计时三秒清零

6 继续选择商品

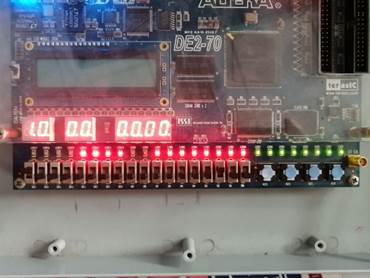

7 选择5元商品

8 投币6元

9 交易成功

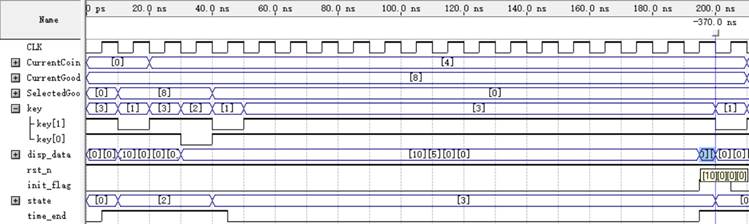

10 仿真波形图一

场景描述:拨动开关选择10元商品——按下confirm确认选择——拨动开关选择5元硬币——按下insert确认投币——按下confirm确认交易——交易失败——指示灯报警——计时三秒清零。

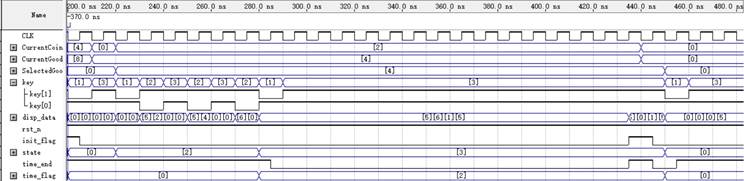

11 仿真波形图二

场景描述:拨动开关选择5元商品——按下confirm确认选择——拨动开关选择2元硬币——按下insert确认投币——按下insert确认投币——按下insert确认投币——按下confirm确认交易——交易成功——指示灯闪烁——计时三秒清零。

五 设计总结

1 问题回顾

问题描述:always敏感列表有三个条件时无法正确得到想要的结果?实际情况为我们想在always敏感列表加入三个条件,一个是复位:检测到时对数据进行清零,一个是检测投币按钮下降沿:检测到时进行投币额累加,一个是检测确认键按钮下降沿:检测到时进行状态变化。整个代码逻辑简单且清晰,一定不会出错,但是实际结果却出现进行投币时按一下投币键累加了n次。

解决思路:

观察现象,发现与按键抖动的情况很像,即按一次键由于抖动在短时间内判断按下了很多次。在网络上搜索各种去抖模块后发现仍然不行,在请教老师后得知板子自带去抖模块,并教导我们先通过灯来看看是否是抖动的原因造成的,后来我们在十进制计数器程序中进行了测试,发现并没有按一次键同时识别到多次的情况。

既然不是抖动的原因,那为什么会造成这种现象?我们从波形仿真的结果进行探究,发现波形仿真中各个值始终为零,与FPGA板实验现象不符合。在板子上明明是可以正常进行操作,只是投币数会计算多次,但是波形仿真却始终为零。我们开始怀疑代码的问题。

通过对代码进行分段注释、换不同的写法并不断波形仿真,最终我们发现是always敏感列表的条件的问题,只要不同时检测确认键和投币键,那么单个功能是可以正常工作的。最终我们将投币功能单独写个always摘出来,整个功能恢复正常。

后来老师说敏感列表如果有一个,那么那个就会被当成时钟,如果有两个那么一个当时钟一个当复位或置位,如果有三个那么一个当时钟,另外两个当复位和置位。我们当时的问题在于想要将确认键和投币键都当作时钟触发always,然而现实中没有与其对应的硬件,即无法综合,会出现意料之外的问题。

2 收获与感想

对于程序的总体设计,应当使用分模块设计,这将使我们的程序耦合性低,也便于小组内的分工,在测试时也可以对于单个模块进行测试,更加有利于问题的定位。

最大的收获是对于如何使用quartus写verilog并进行仿真、下载更加熟练,对于verilog各种语法和坑点有了更多的了解。仿真的时候可能不会出错,但是实际综合的时候却不一定。要牢牢记住的是,verilog是硬件语言,并不是说语法没错就能得到想要的结果,而是立足于现实硬件,如果没有对应的硬件,那么就是不可综合的,人们称之为硬件的魅力。